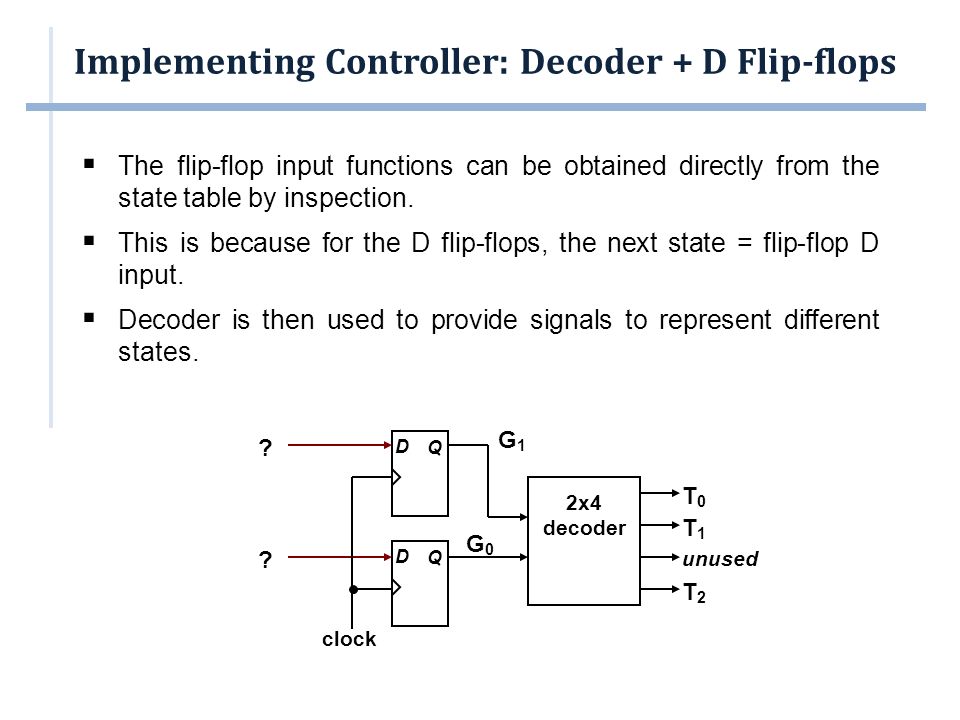

Figure 10 from An ultra-low power wake up receiver with flip flops based address decoder | Semantic Scholar

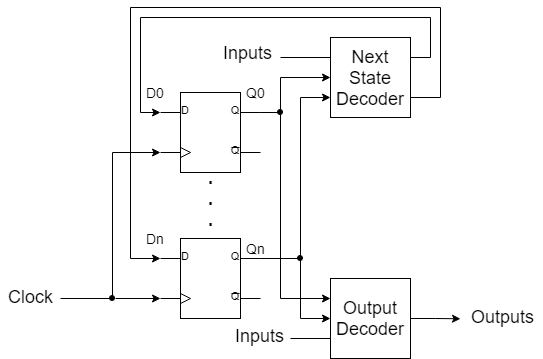

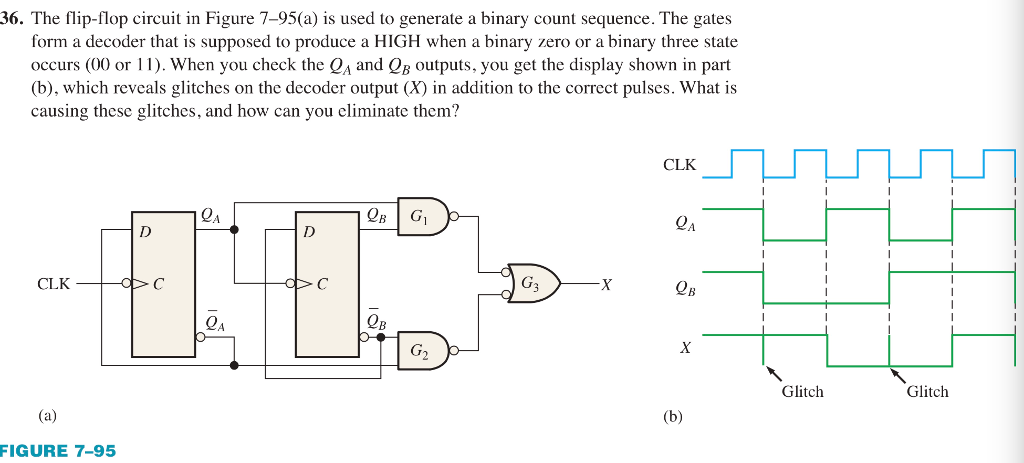

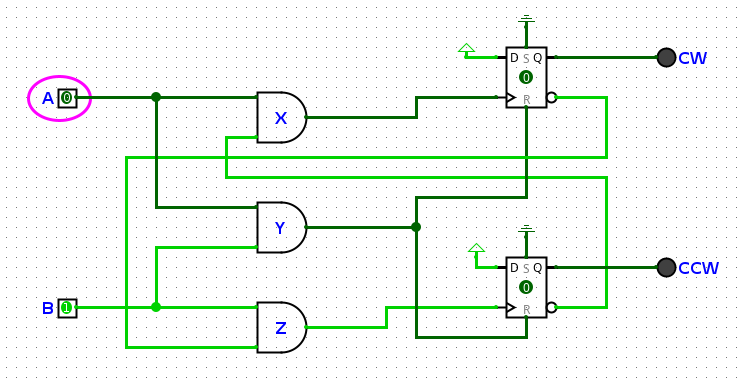

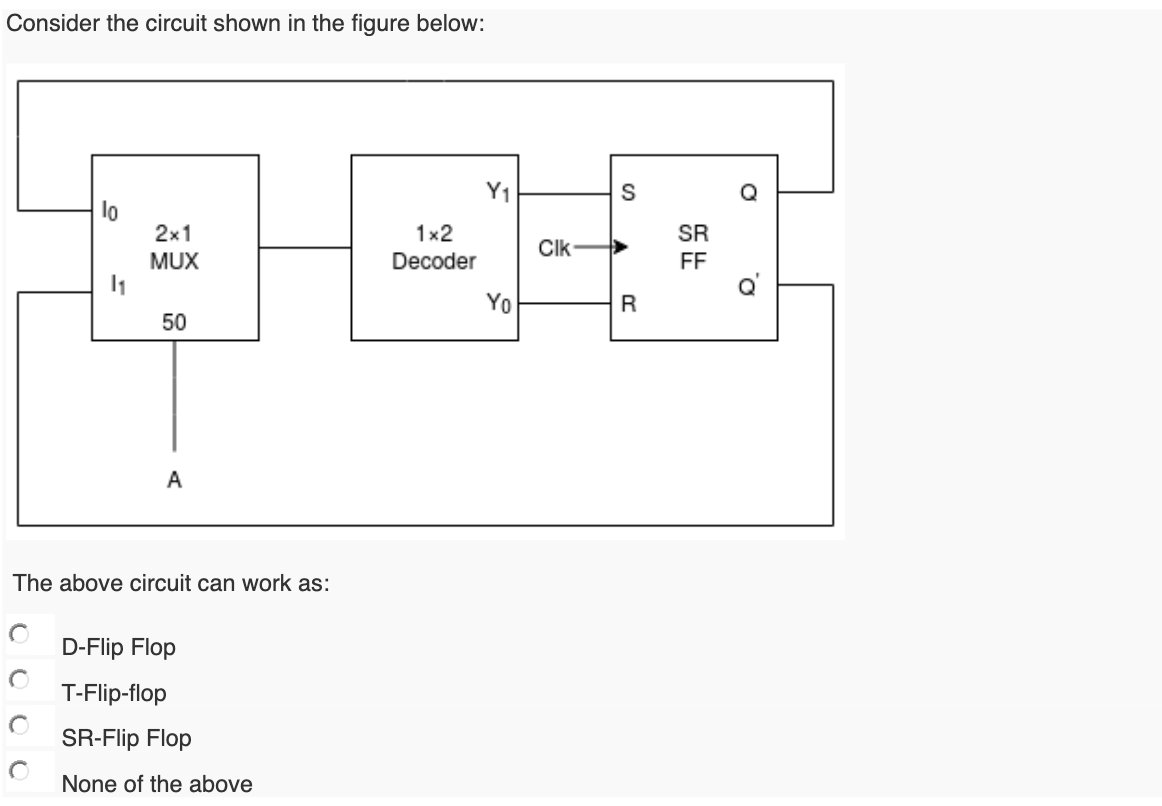

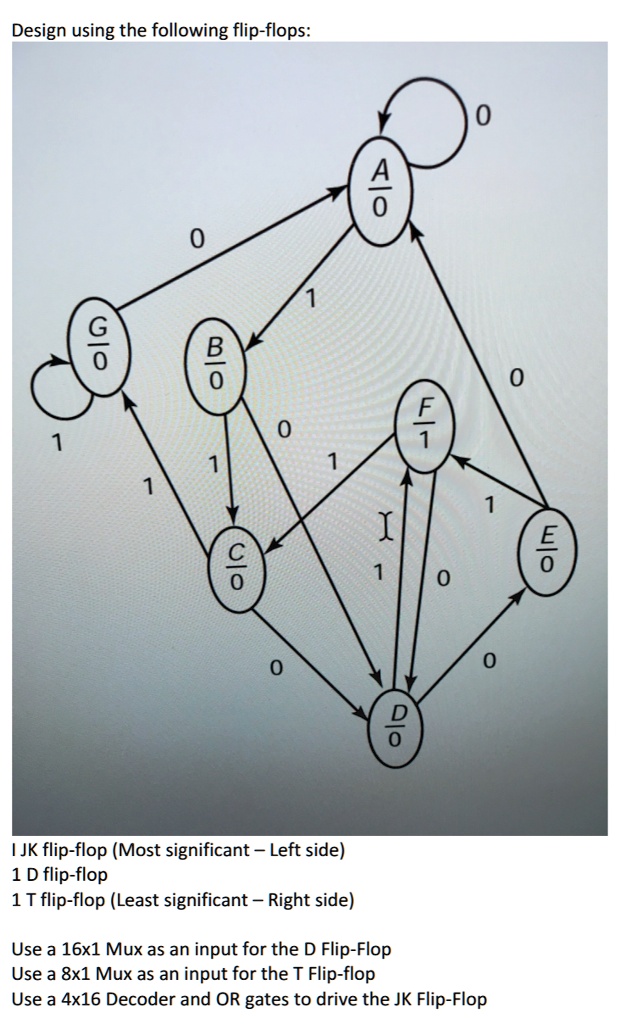

SOLVED: Design using the following flip-flops: 0 G 10 B 10 0 1 0 1 1 1 1 0 0 0 I. JK flip-flop (Most significant - Left side) II. D flip-flop