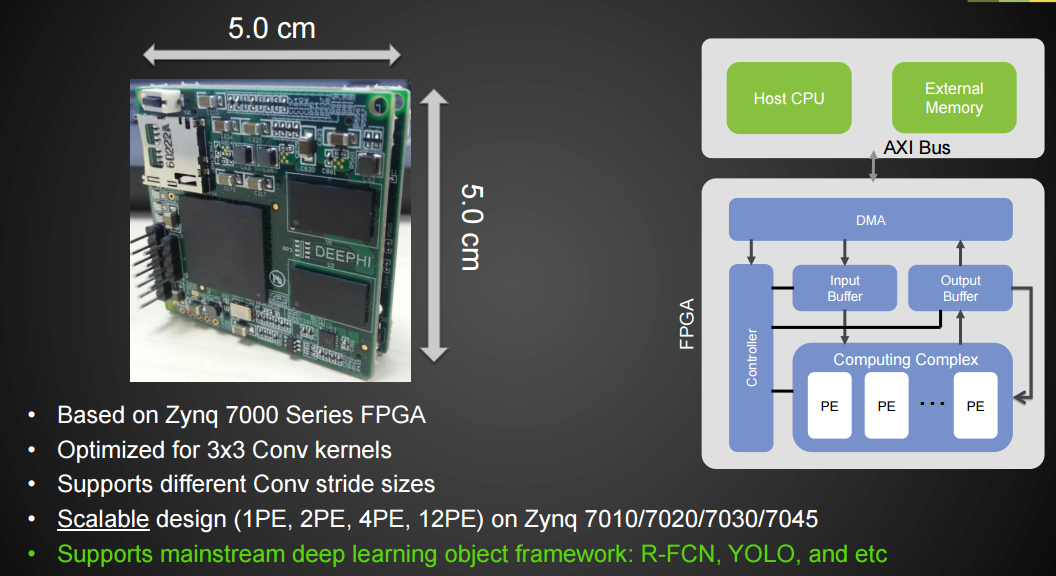

GitHub - coleblackman/TIDENet: TIDENet is an ASIC written in Verilog for Tiny Image Detection at Edge with neural networks (TIDENet) using DNNWeaver 2.0, the Google SkyWater PDK, OpenLANE, and Caravel.

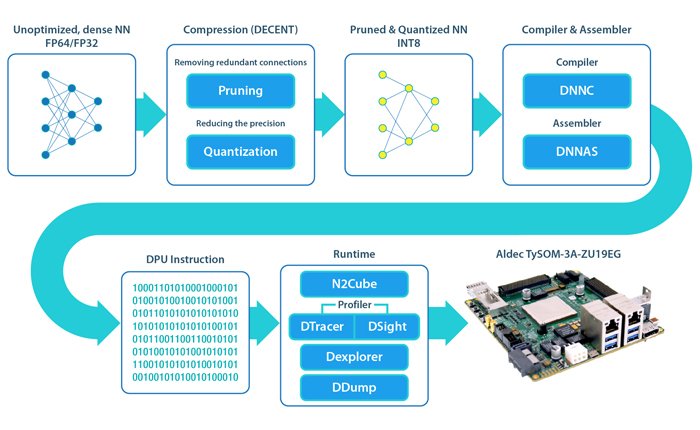

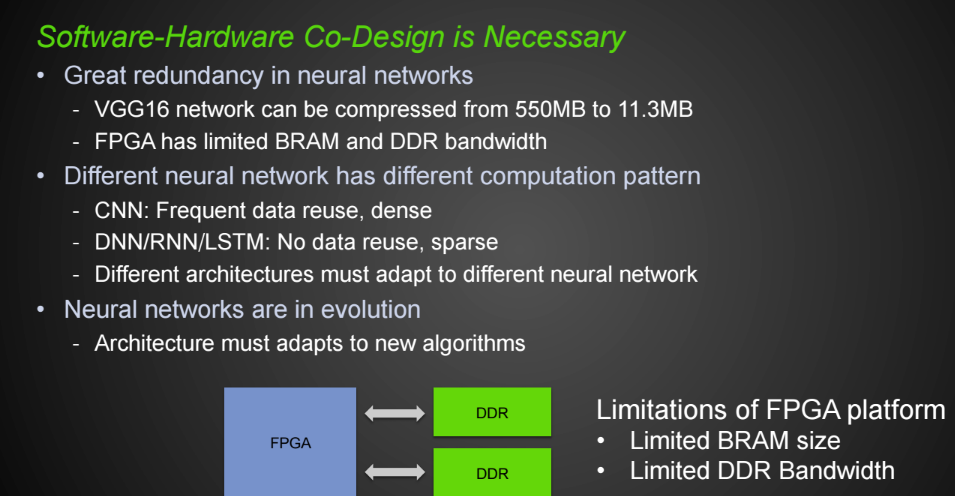

How to develop high-performance deep neural network object detection/recognition applications for FPGA-based edge devices - Blog - Company - Aldec

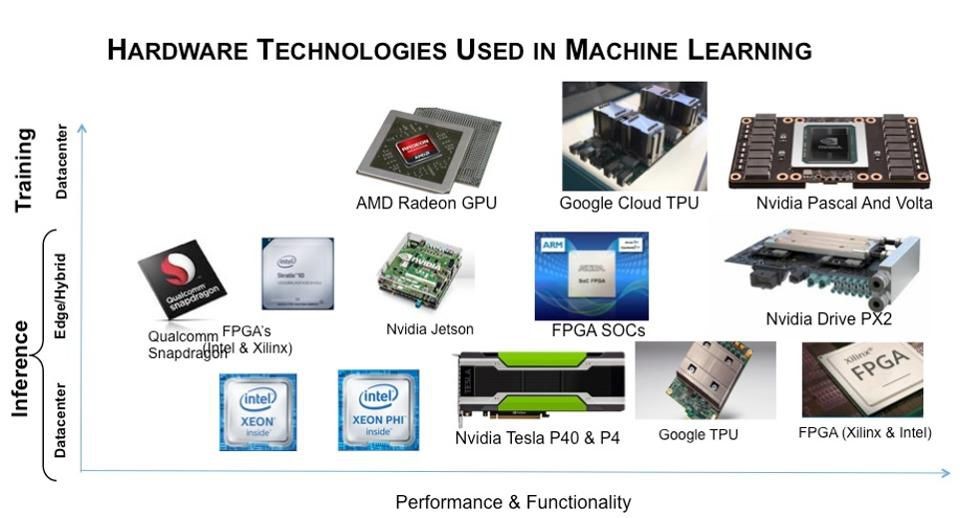

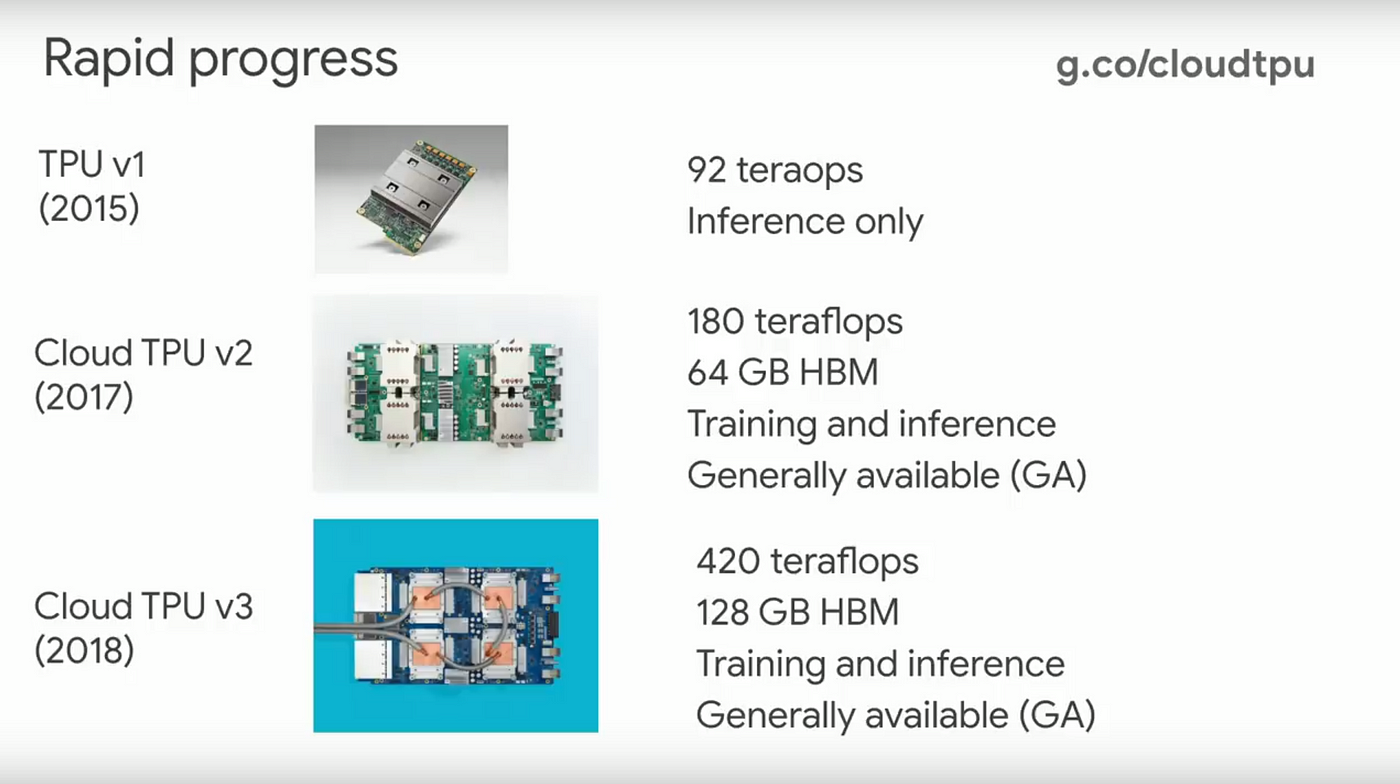

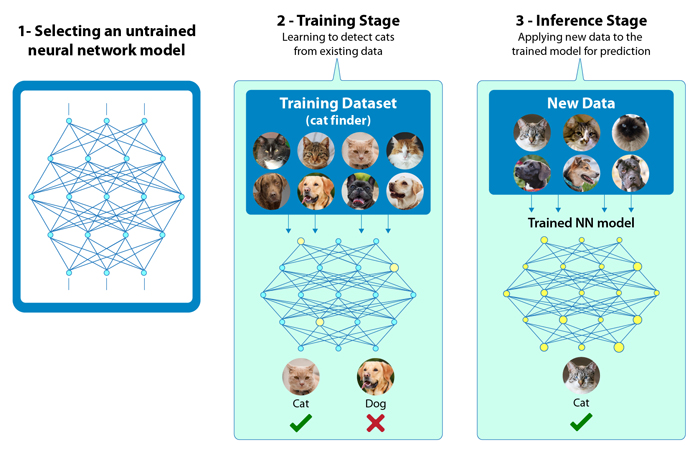

The Deep Learning Inference Acceleration Blog Series — Part 2- Hardware | by Amnon Geifman | Towards Data Science

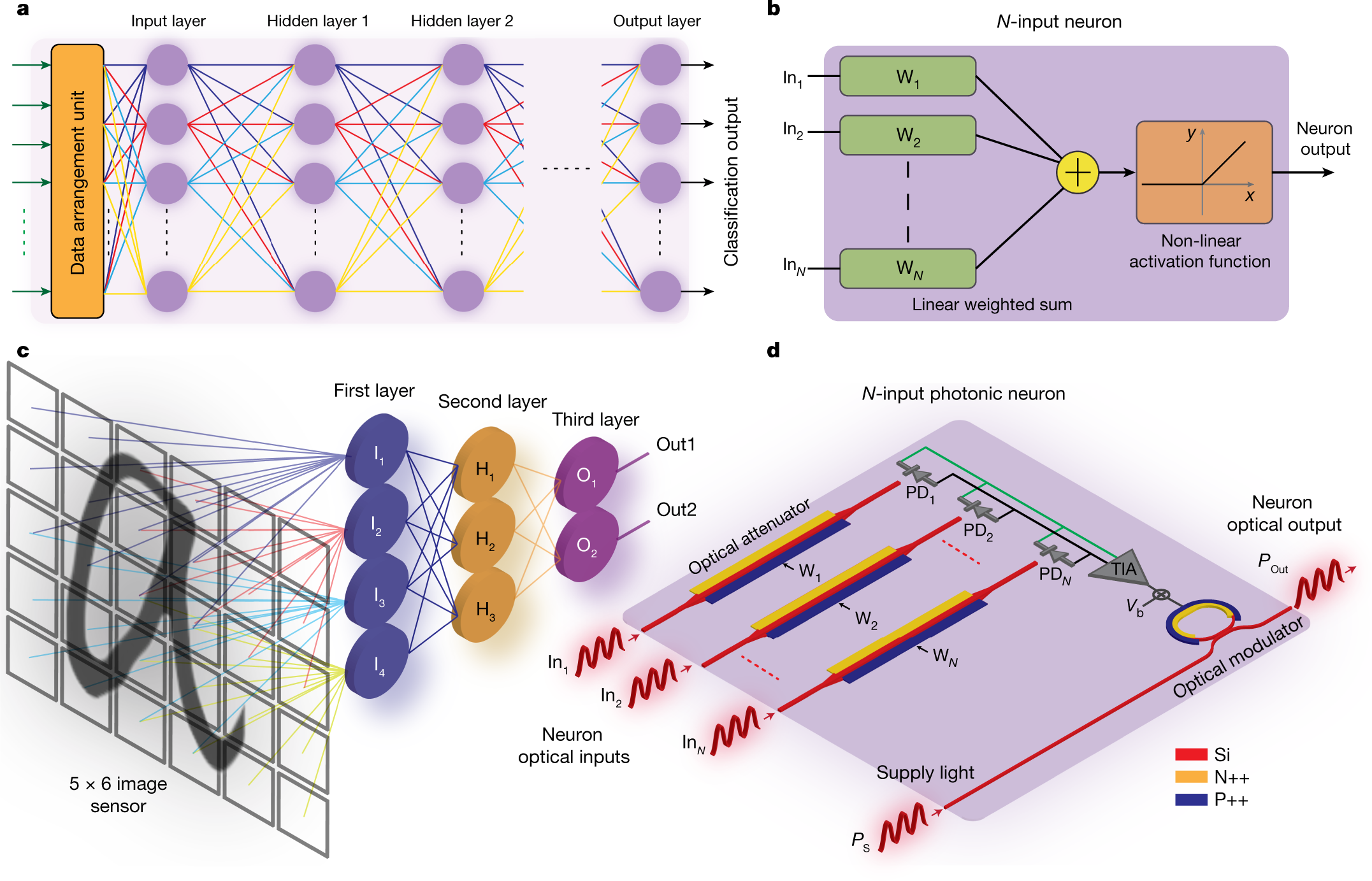

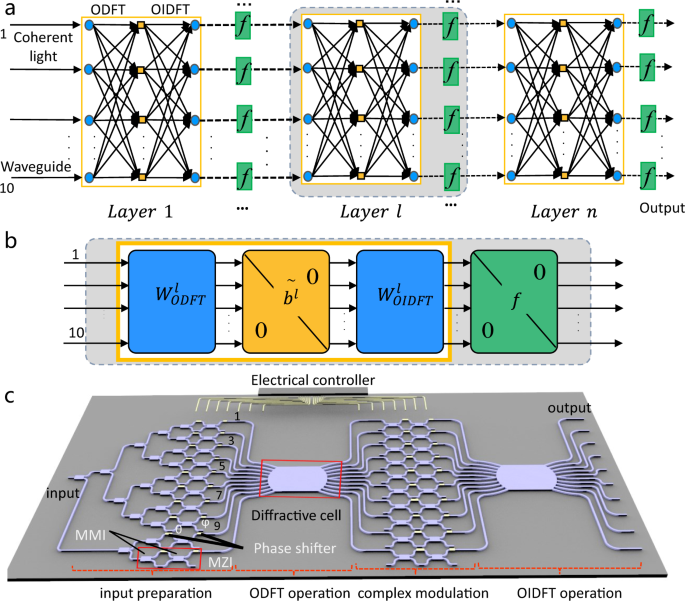

Space-efficient optical computing with an integrated chip diffractive neural network | Nature Communications

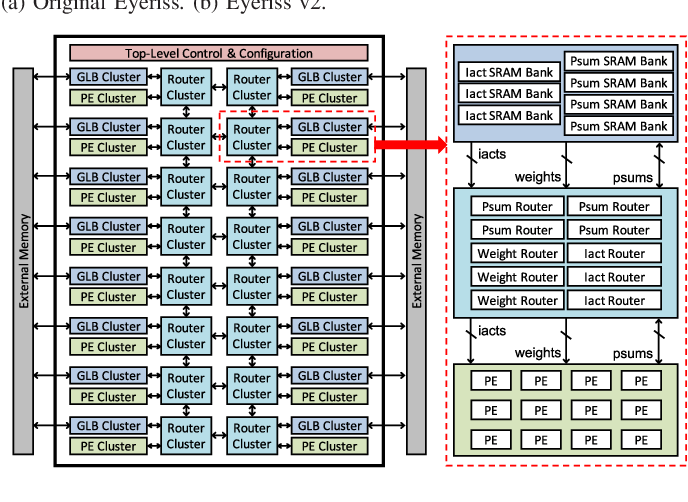

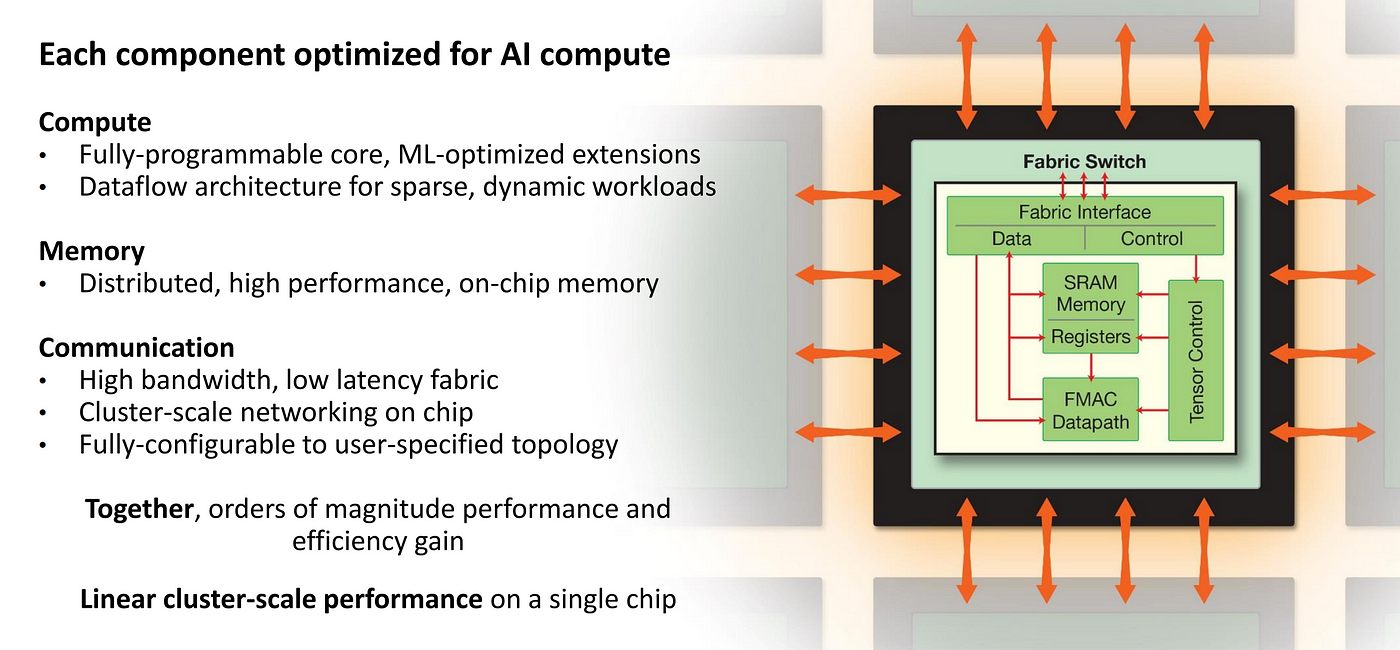

The New Deep Learning Memory Architectures You Should Know About — eSilicon Technical Article | ChipEstimate.com

Deep Neural Network ASICs The Ultimate Step-By-Step Guide: Gerardus Blokdyk: 9780655403975: Textbooks: Amazon Canada

Arch-Net: A Family Of Neural Networks Built With Operators To Bridge The Gap Between Computer Architecture of ASIC Chips And Neural Network Model Architectures - MarkTechPost