Solved: Chapter 9 Problem 18P Solution | Digital Design With Cpld Applications And Vhdl 2nd Edition | Chegg.com

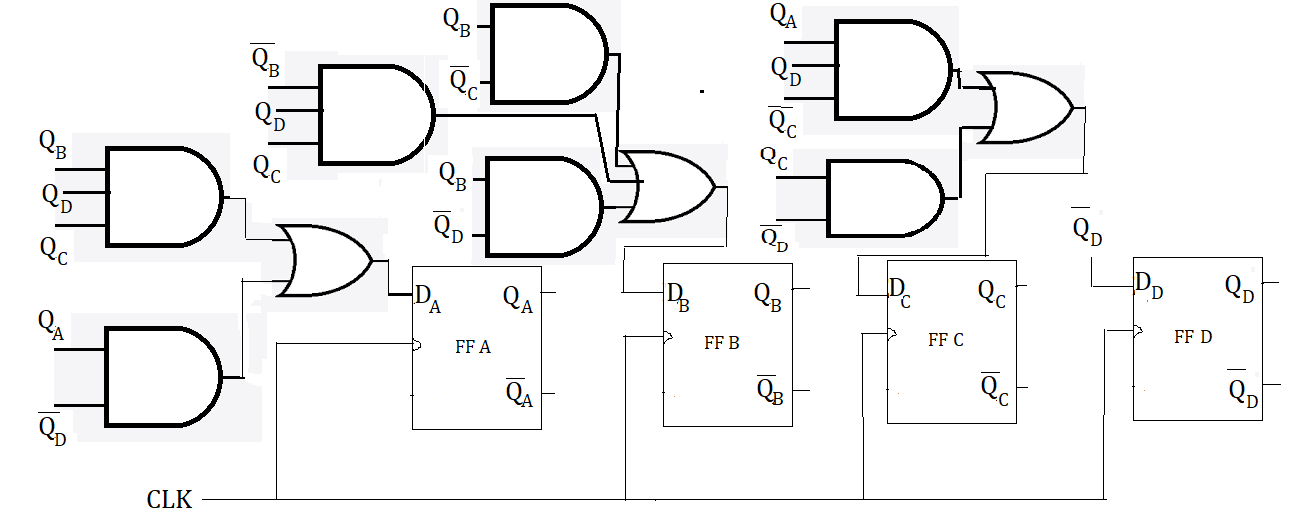

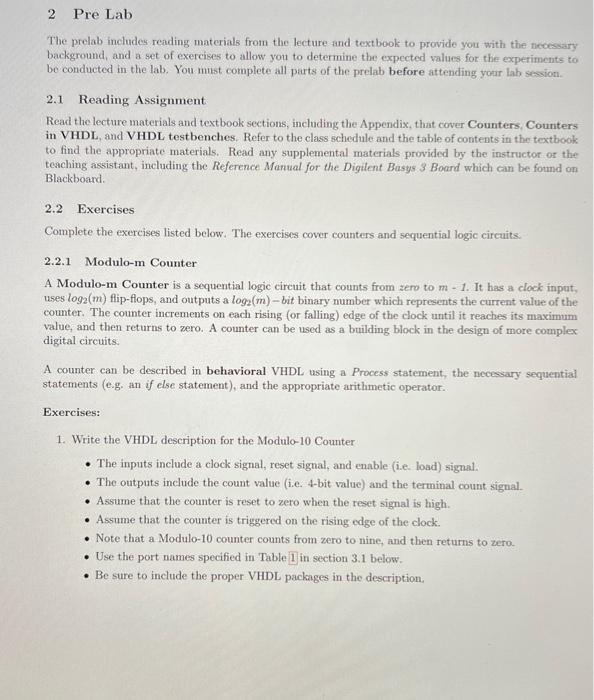

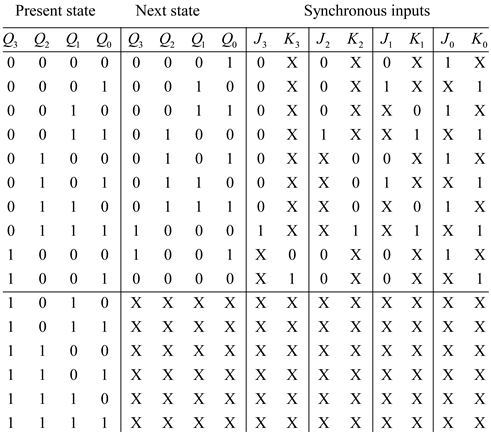

Design mod-10 synchronous counter using JK Flip Flops.Check for the lock out condition.If so,how the lock-out condition can be avoided? Draw the neat state diagram and circuit diagram with Flip Flops.

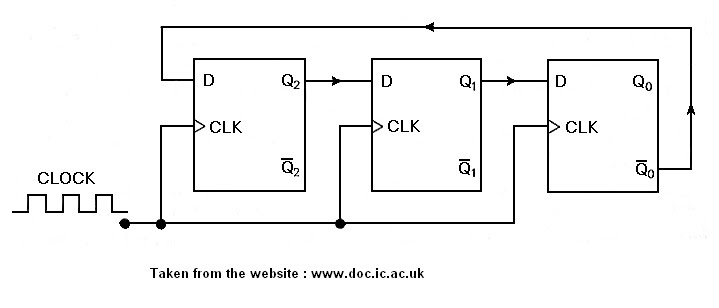

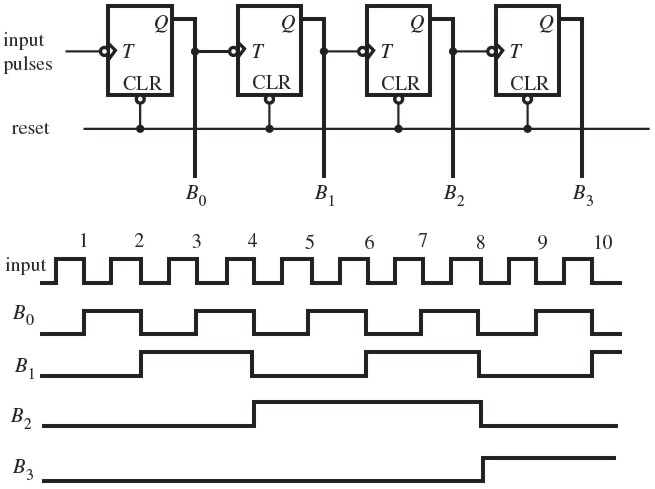

SOLVED: Show how you can design a MOD-10 asynchronous counter using J-K flip flops. 10 decoder CLR FF0 FF1 FF2 FF3 D0 D1 D2 CLK C>C D3 E CLR CLR CLR CLR

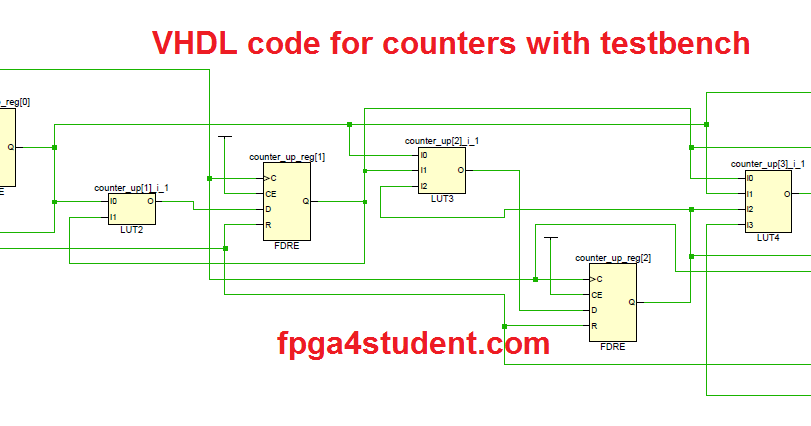

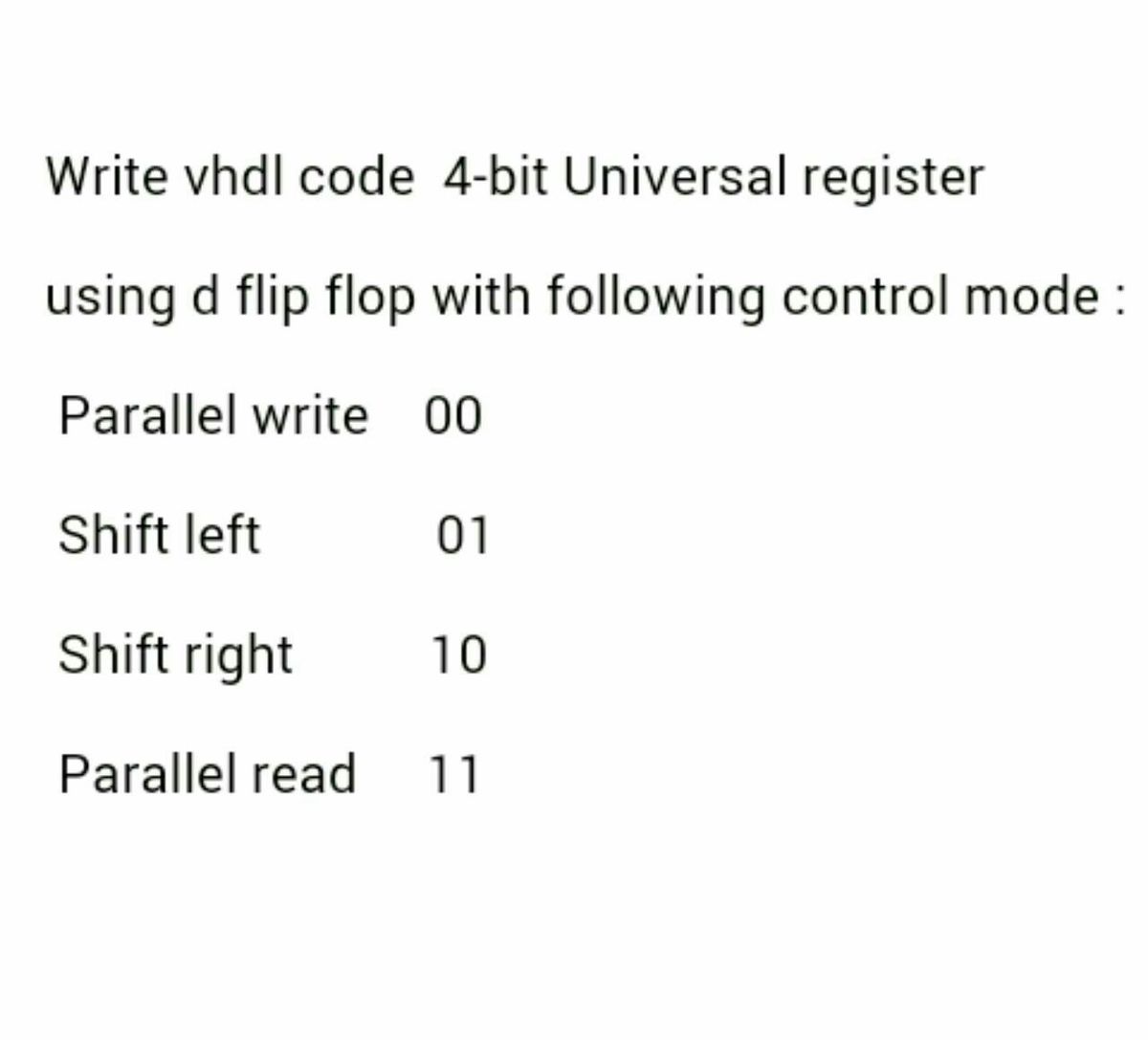

SOLVED: a. To design a mod-10 counter, you need an n-bit register. What is n? b. Write a VHDL code for a mod-10 counter using design techniques that we studied in class.

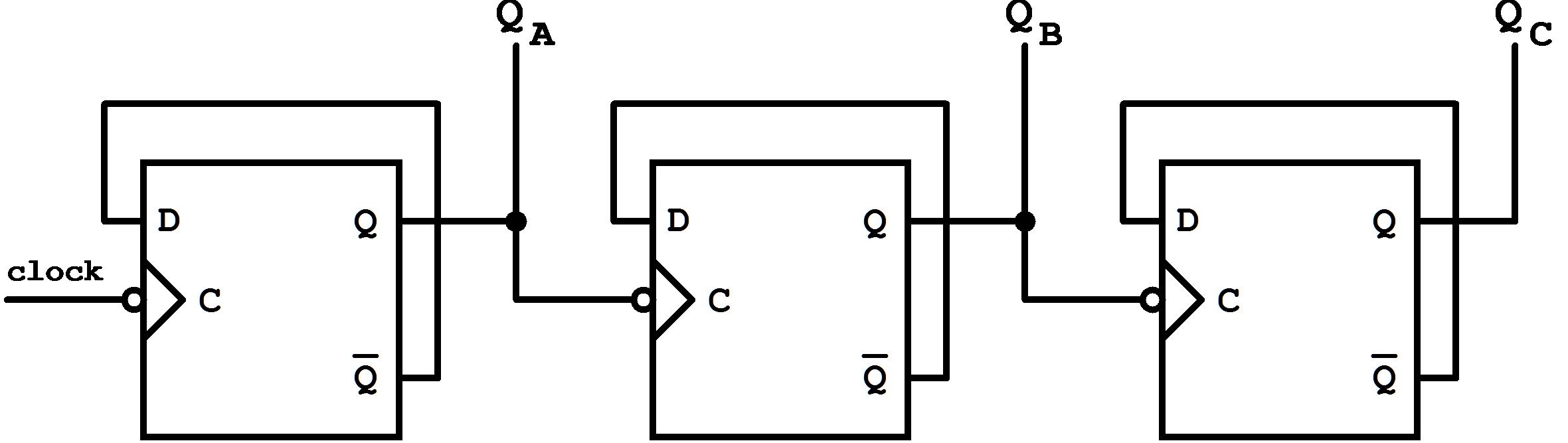

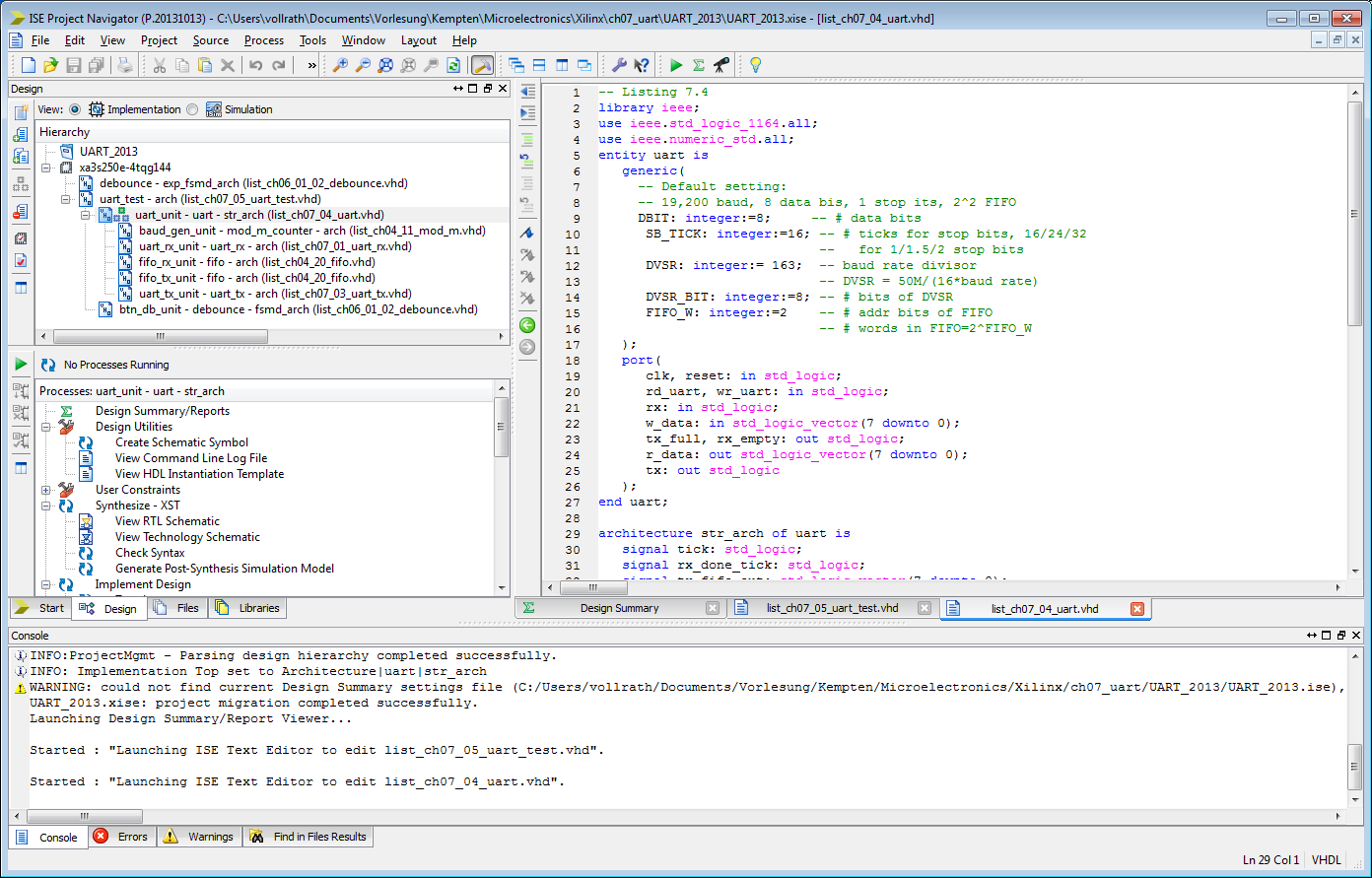

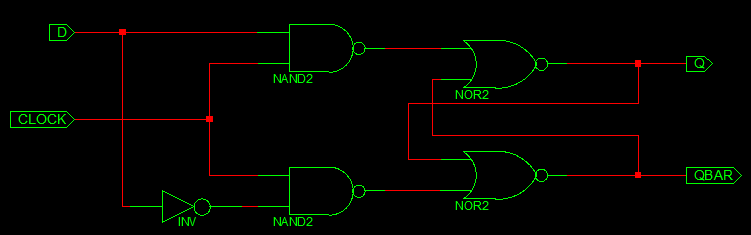

lesson 34 Up Down Counter Synchronous Circuit using D Flip Flops in VHDL with and with reset input - YouTube